XFdtdを用いたESD試験と損傷予測

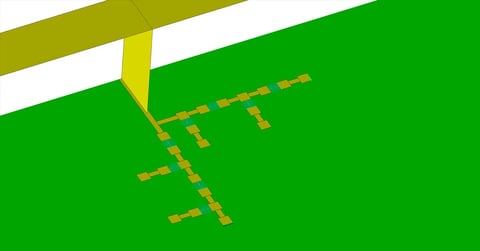

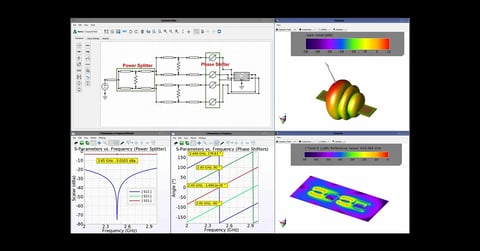

XFdtd® 電磁界シミュレーションソフトウェア 静電気放電(ESD)試験をシミュレートすることで、エンジニアは静電気放電が発生する可能性のある場所を特定することができます。 絶縁破壊 デバイスの設計において、損傷リスクのある部品やコンポーネントを特定することができます。This webinar introduces XF’s collection of ESD simulation features and demonstrates how to minimize the chance of undetected damage prior to hardware testing.

XFdtd® 電磁界シミュレーションソフトウェア 静電気放電(ESD)試験をシミュレートすることで、エンジニアは静電気放電が発生する可能性のある場所を特定することができます。 絶縁破壊 デバイスの設計において、損傷リスクのある部品やコンポーネントを特定することができます。This webinar introduces XF’s collection of ESD simulation features and demonstrates how to minimize the chance of undetected damage prior to hardware testing.

概要

ESD 試験は、電子機器メーカーが自社のデバイスの ESD 感受性を判定するために世界中で利用 されています。年間 ESD 損失の正確なコストを見積もることは極めて困難ですが、ESD が多くのハードウェア試作品の開 発と試験を必要とし、顧客の手元で故障が発生した場合、多くの保証クレームや消費者の信頼失墜につながると言 えるでしょう。

ESD ハードウェア・テストにかかる時間と材料費の高コストを考慮すると、XFdtdで ESD テスト・プロセスをシミュレートできる機能は非常に貴重です。これにより、エンジニアは製品開発のコンセプトおよび設計段階で、ESD 損傷の影響を受けやすい箇所を特定し、ESD 軽減策を最適化することができます。