EM解析プロジェクトを簡素化する当社の製品についてご覧ください。

リソース・ライブラリーを見る最新ニュースを購読する

関連リソース

出版物

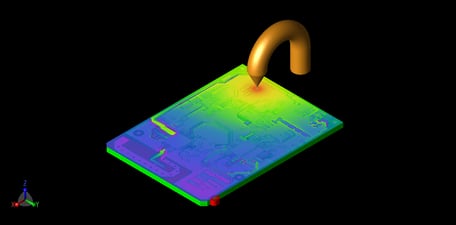

設計された電磁面を用いた無線カバレージ拡張の光線光学モデリング:28 GHzにおける実験的検証

本論文では、EESの新しい光線散乱モデルの精度を検証するために実施した伝搬実験の結果を示す。

探索 リソース

出版物

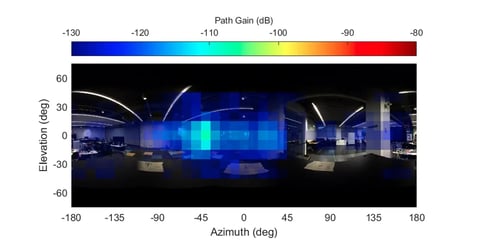

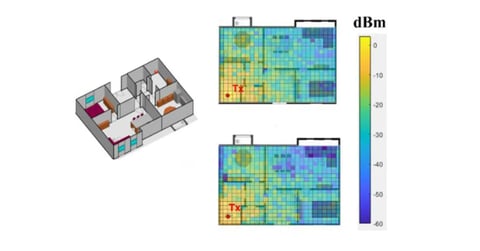

画像処理、幾何光学、輸送理論に基づく60GHzにおける高速屋内カバレッジ予測スキーム

本論文では、デジタル画像処理、幾何光学、輸送理論を用いて、室内経路損失の高速かつ近似的な予測方式を開発する。

探索 リソース