導波管クロス結合フィルターのシミュレーション

この例では、クロス・カップリング・フィルタ[1]の複雑な構造において、XFdtdを用いて導波管ポート・ソースを追加した例を示します。このフィルタ構造は、WR-90 導波路をタイトなカーブに折り曲げたもので、カーブの曲がり角にアパーチャ結合キャビティがあります。導波管内にもいくつかのアイリスが挿入されている。設計手順の詳細は論文に記載されている。

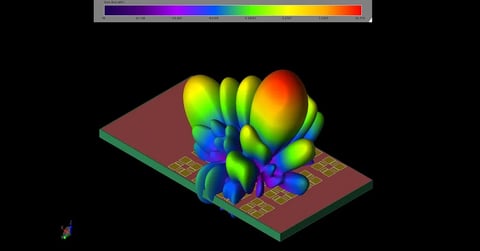

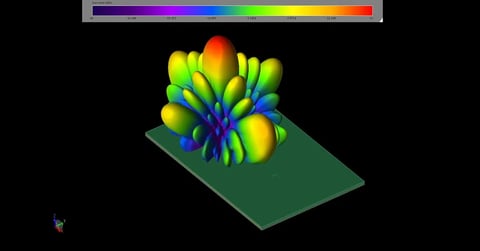

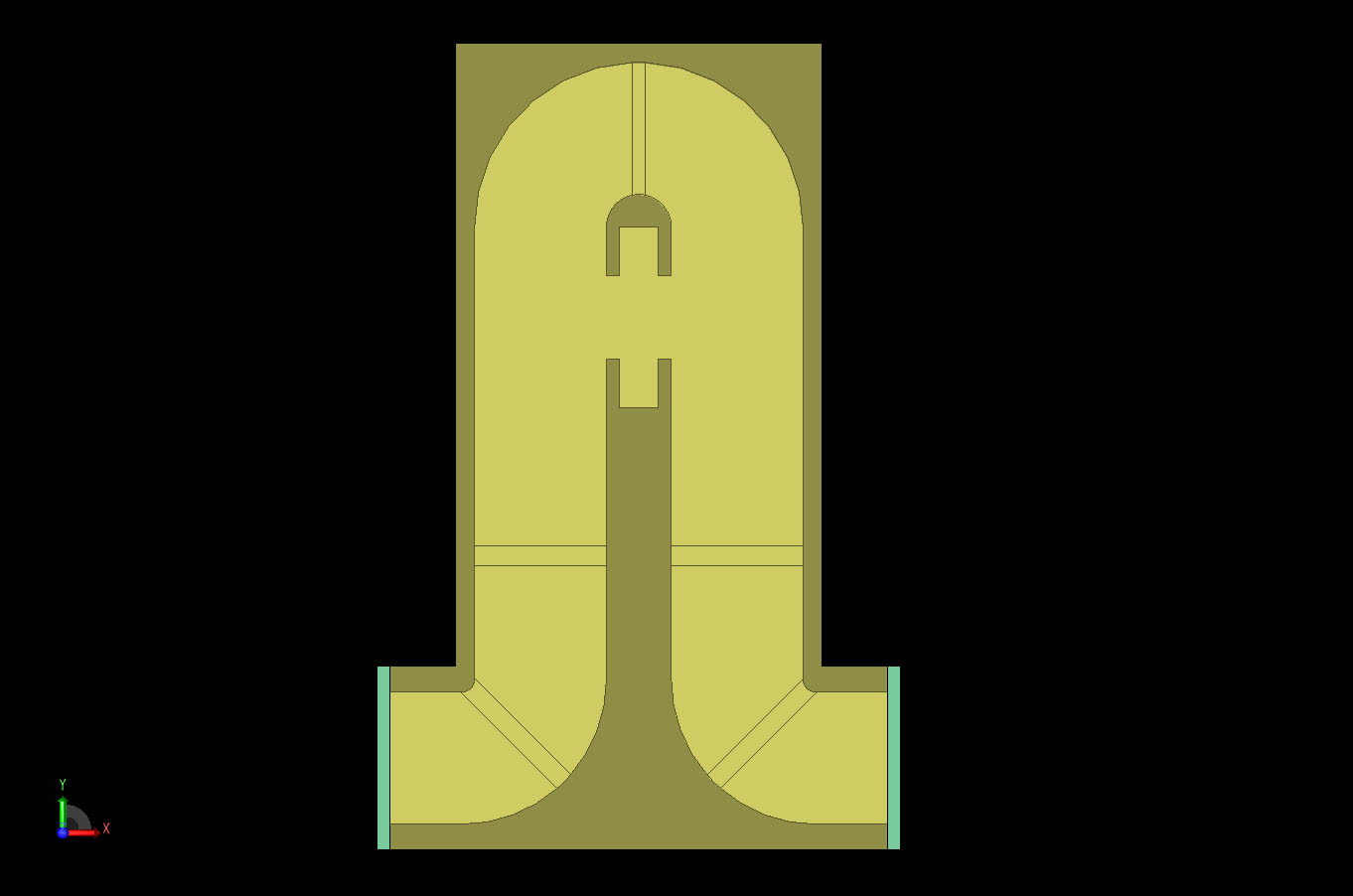

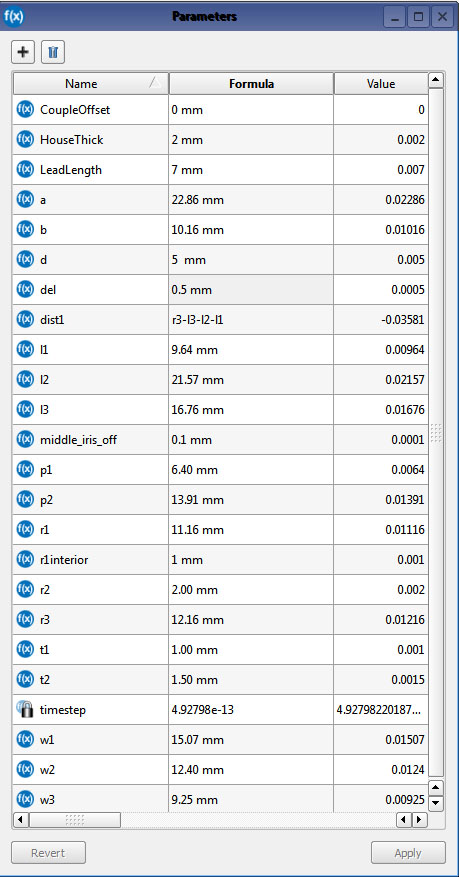

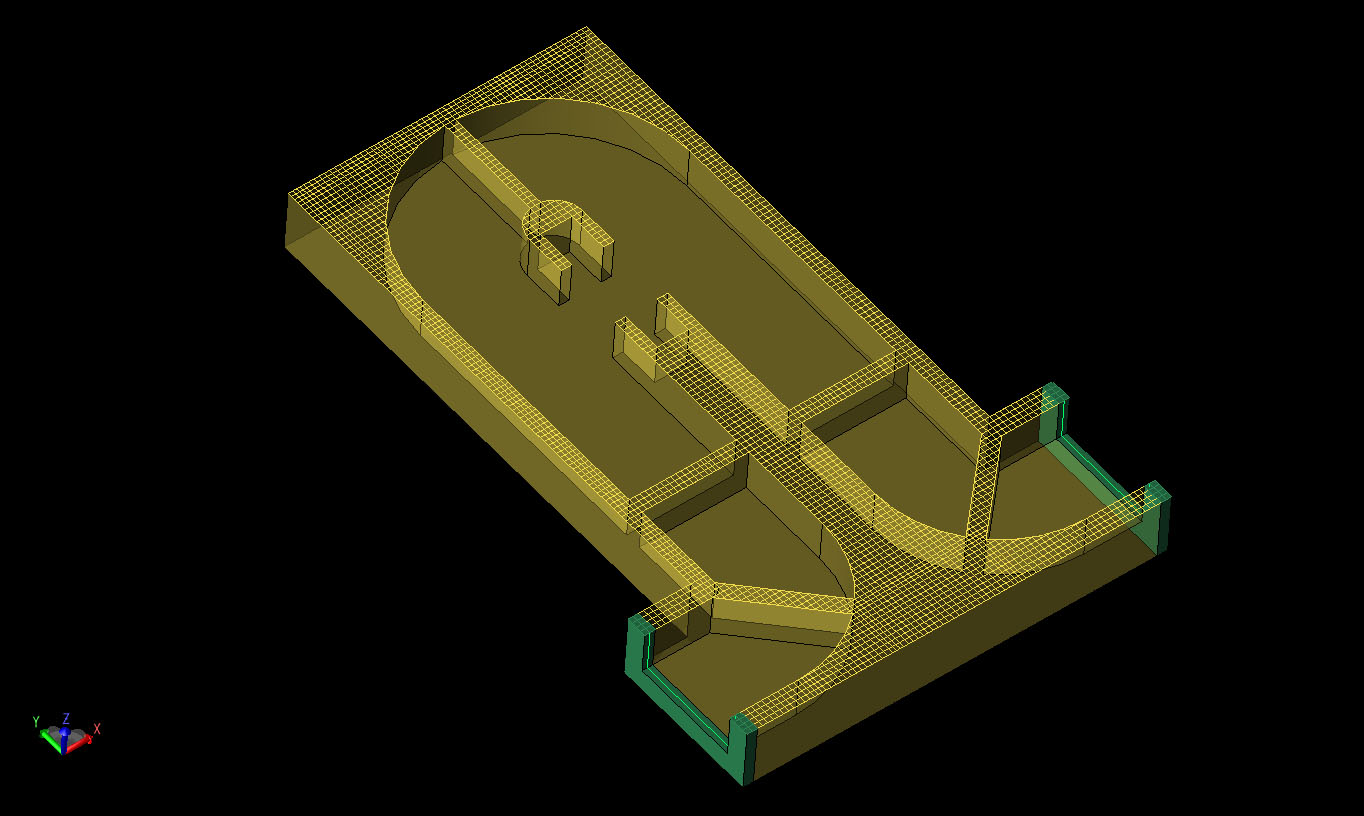

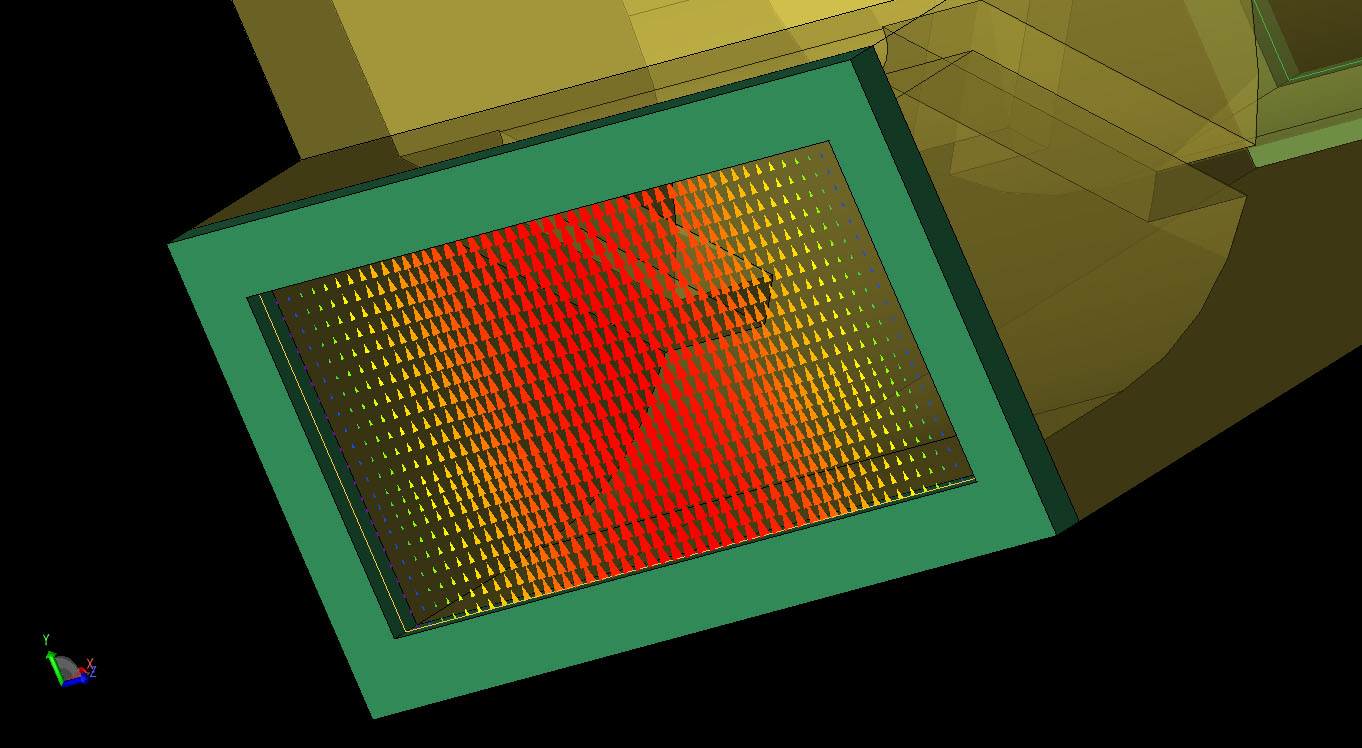

XFdtd シミュレーションでは、まず図 1 に示すような構造を CAD モデルとして作成します。構造の黄色い部分が導波管フィルターで、端にある 2 つの緑色の長方形が導波管ポートの位置を表しています。この構造は、論文で定義された各寸法のパラメータリストに基づいて作成され、図2に示されています。このシミュレーションでは、0.5 mm のグローバルメッシュを使用し、曲線導波路部分にはXACT Accurate Cell Technologyメッシングを、導波路ポートには Fixed Points メッシングを適用しています。この構成により、メッシュサイズが変化し、各形状フィーチャーのエッジにグリッド線が正確に配置されます。出来上がったメッシュの断面を図 3 に示します。

図1:導波管クロスカップリング・フィルターの形状をCADで表したもの。

図2:クロスカップル・フィルター形状で使用されるすべての寸法のXFdtdパラメーターリスト。

図3:クロスカップル・フィルター形状のXFdtdメッシュの断面図。

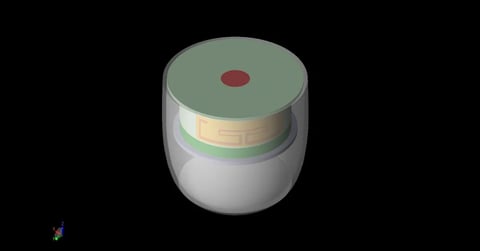

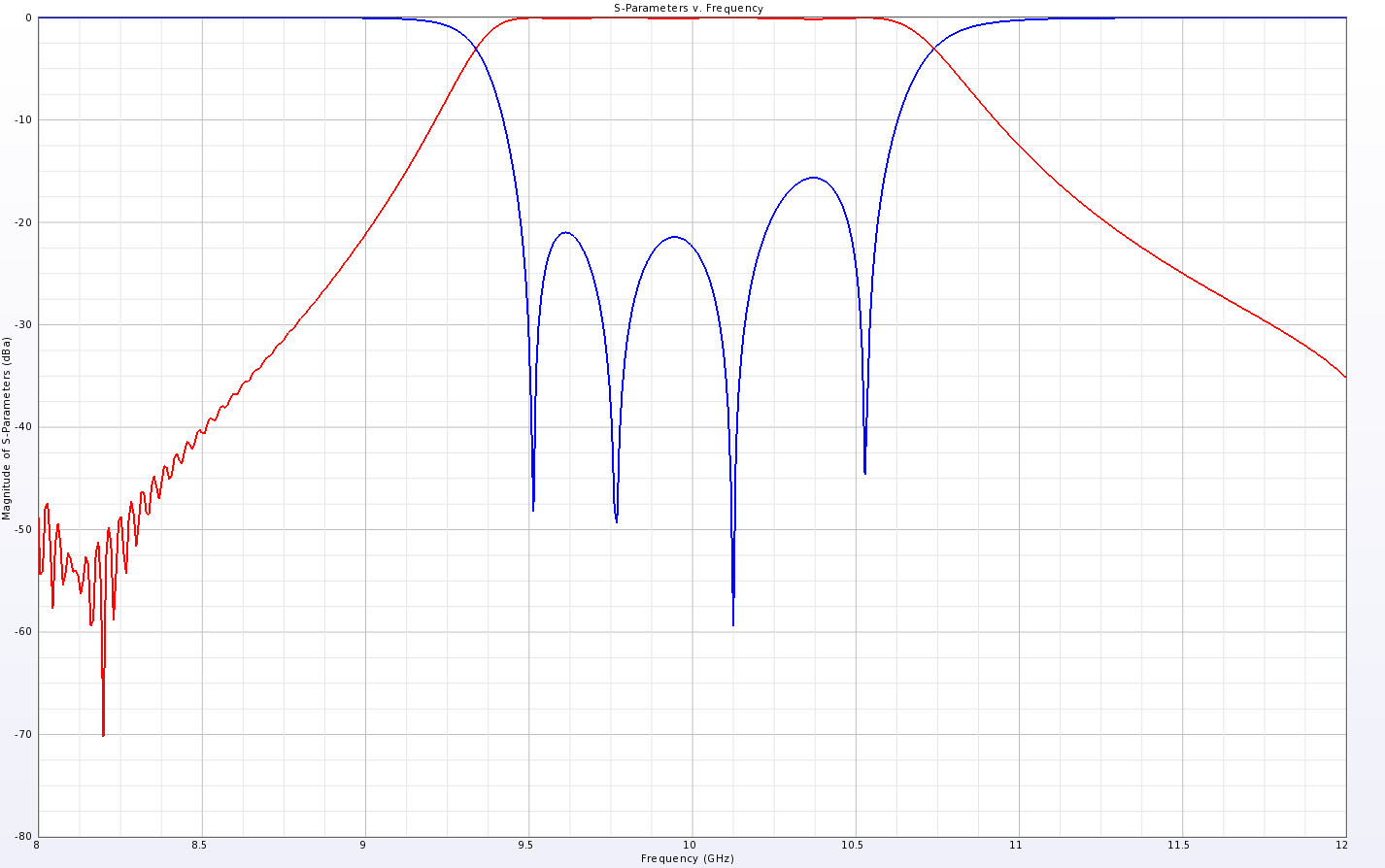

ポートは導波管の開口部を横切って追加され、入力ポートについては図 4 に示すように、分布は TE10 モードとして設定される。シミュレーションは、デバイスの 8~12 GHz の周波数範囲の入力波形で実行されます。45dB に収束するまでの時間は,NVIDIA C1060 Tesla GPU カードで約 15 分です.シミュレーション後、入力ポートと出力ポートのSパラメータが得られ、図5に表示されます。

図4:デバイスの入力ポートに印加されたTE10導波管ポート励起。

図5:クロスカップル・フィルター形状のS11とS21の計算結果。

参考文献

-

Q.F. Zhang and Y. L. Lu, "Dimensional Synthesis of Symmetric Wideband Waveguide Cross-Coupled Filters Without Global Full-Wave Optimization,"IEEE Trans.Microw.Theory Tech., Vol.58, Dec. 2010, pp.3742-3748.

プロジェクトファイルのリクエスト

このアプリケーション例にご関心をお寄せいただき、ありがとうございます。導波管クロスカップルフィルタシミュレーションのプロジェクトファイルをダウンロードするには、以下のフォームにご記入ください。