- アプリケーション

- ESD試験

ー静電気放電試験と

静電気放電試験は、電子機器メーカーがデバイスの ESD 感受性を判定するために世界中で利用し ています。年間 ESD 損失の正確なコストを見積もることは非常に困難ですが、ESD は多くのハードウェア試作品の開発および試験を必要とし、顧客の手元で故障が発生した場合、多くの保証クレームや消費者の信頼喪失の一因となることは間違いありません。

ESD ハードウェア・テストにかかる時間と材料費の高コストを考えると、XFdtd で ESD テスト・プロセスをシミュレートできる機能は非常に貴重です。XFdtdの静電気放電テスト・シミュレーションを活用することで、エンジニアはESDによるダメージを受けやすい箇所をピンポイントで特定し、製品開発のコンセプトおよび設計段階でESD緩和策を最適化することができます。

XFdtd 3D電磁場シミュレーションソフトウェアによるESD試験シミュレーション

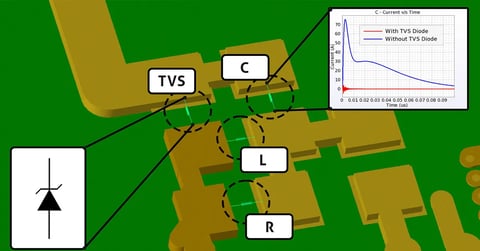

TVSダイオード

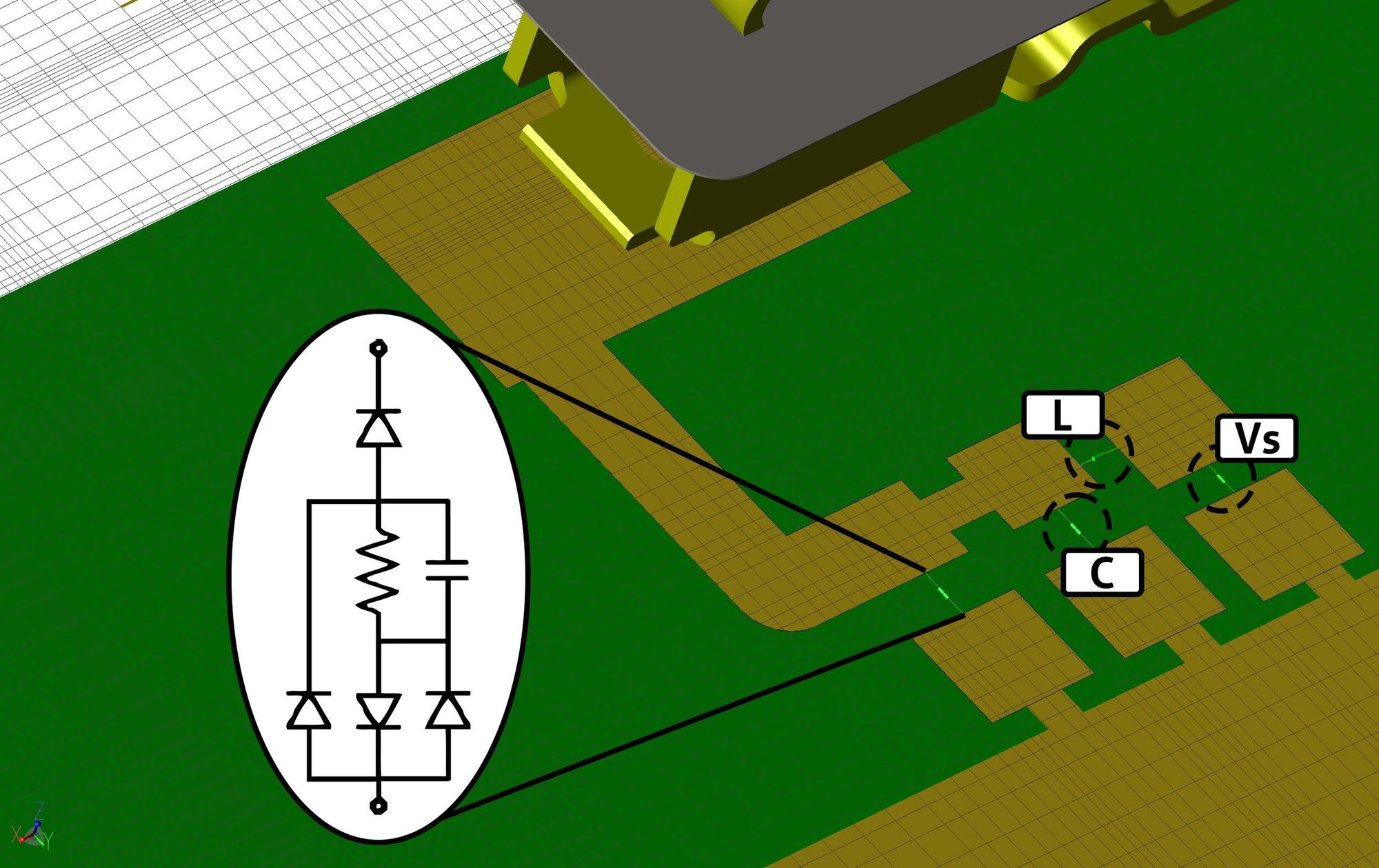

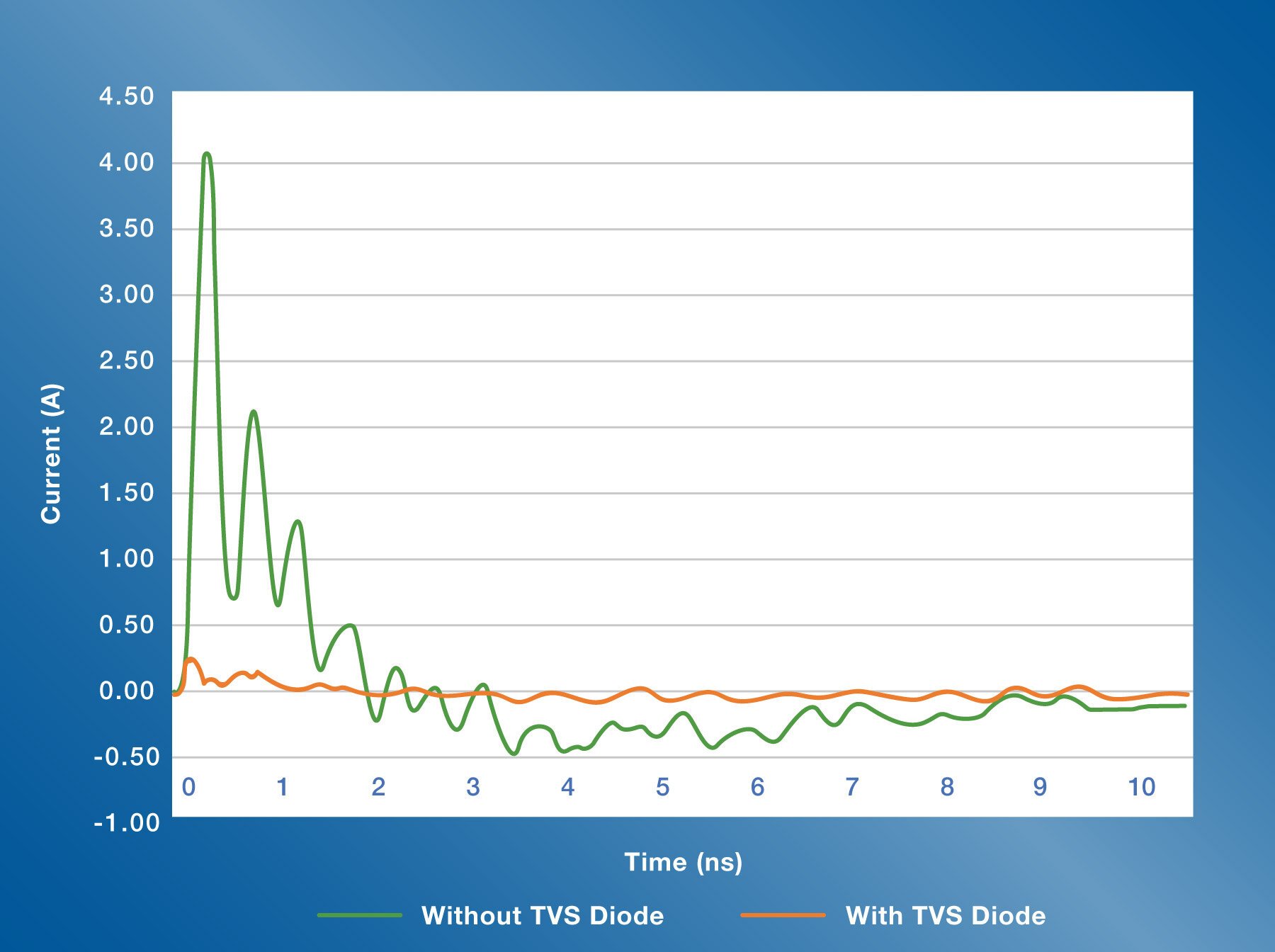

集積回路は、デバイスのRFフロントエンド(RFFE)に普及してきている。集積回路はより多くの機能をサポートする一方で、小型化も進んでいる。その結果、ESD イベントや劣化の影響を受けやすくなっています。TVS ダイオードやその他の非線形 ESD 緩和コンポーネントは、高感度回路を保護し、強い ESD 信号を RFFE に到達する前にグランドにリダイレクトします。XFdtdの過渡EM/回路コ・シミュレーション機能により、これらのデバイスを全波環境でシミュレーションし、システムレベルの解析を実行することができます。

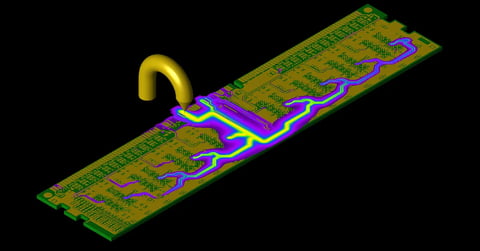

絶縁破壊予測

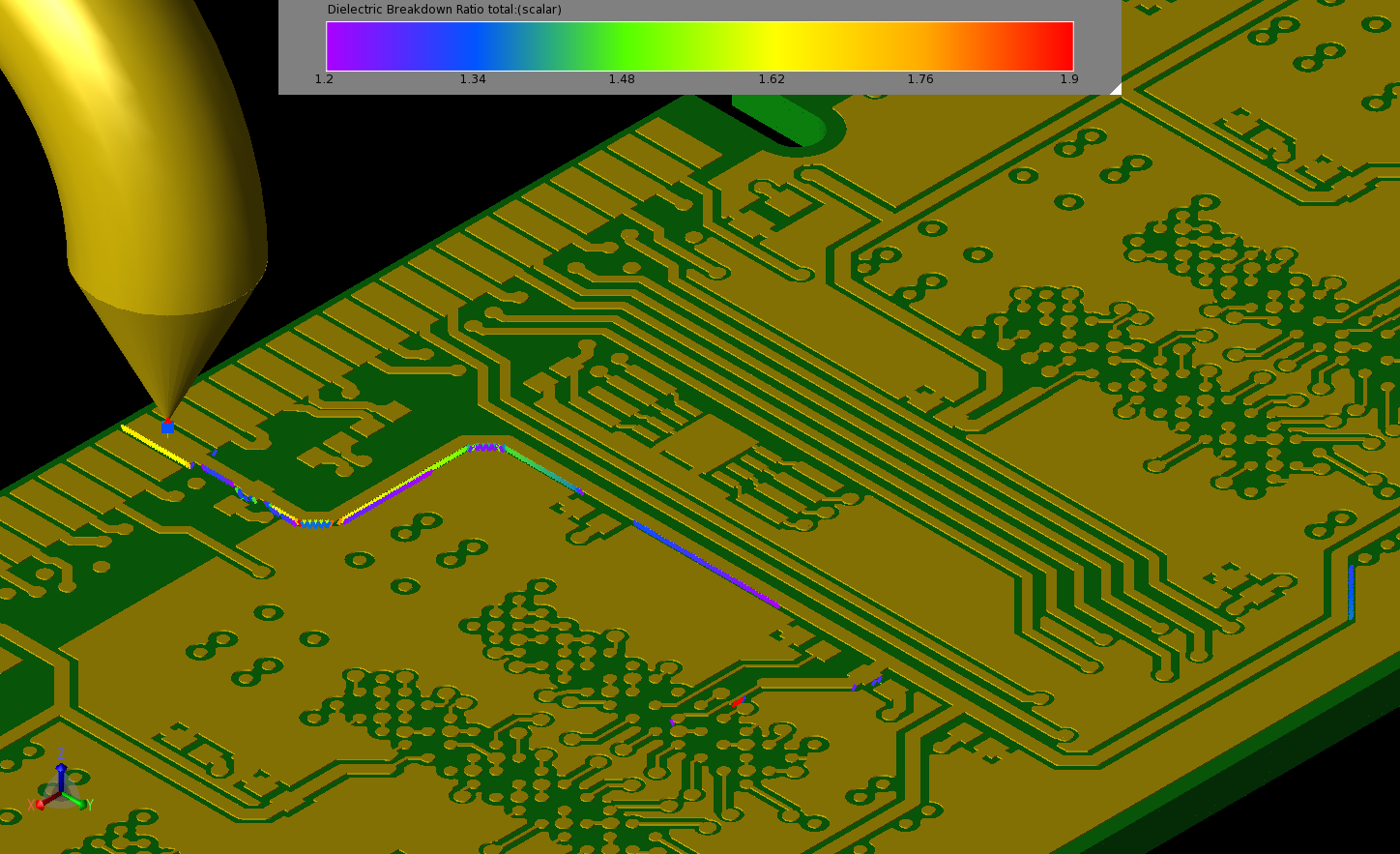

経験豊富な技術者であっても、試験中に ESD 不具合の発生箇所を特定したり、場合によっては不 具合が発生したかどうかを判断することは非常に困難です。これを解決するために、XFdtdでは材料の絶縁耐力を定義することができます。材料の絶縁耐力は、絶縁破壊(絶縁特性を失うこと)を起こすことなく耐えられる最大電界を定義します。XFdtdプロジェクトに材料の絶縁耐力を追加すると、誘電破壊ニアフィールドセンサーを使用して、過渡シミュレーション中にFDTDセルエッジの絶縁破壊の可能性を監視することができます。XFdtdシミュレーションの終了時に、誘電強度を超えたセルエッジを簡単に見つけることができます。

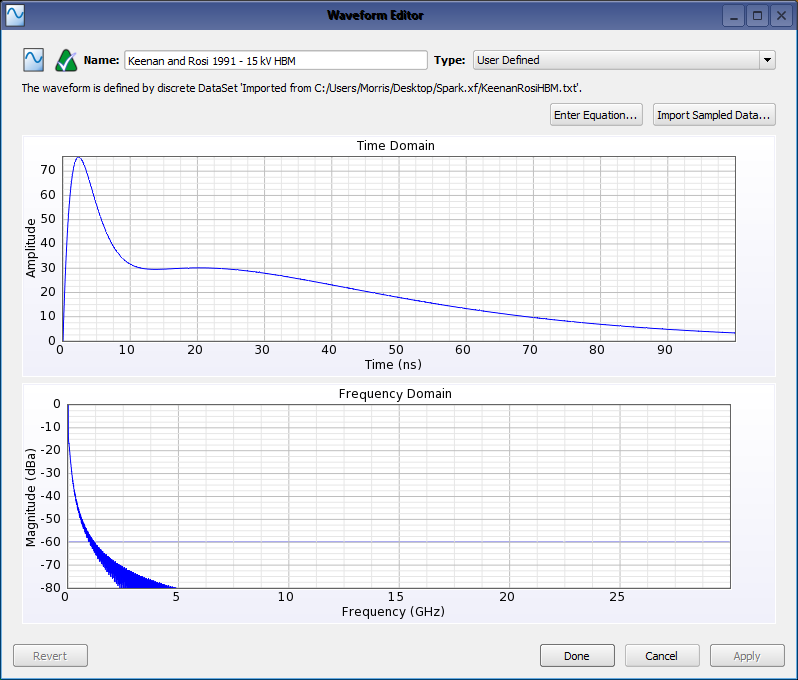

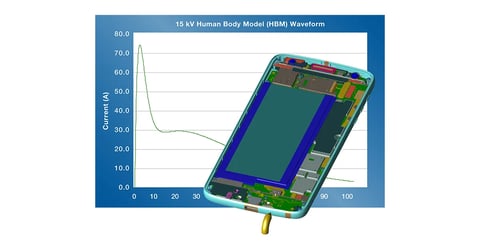

ESD波形

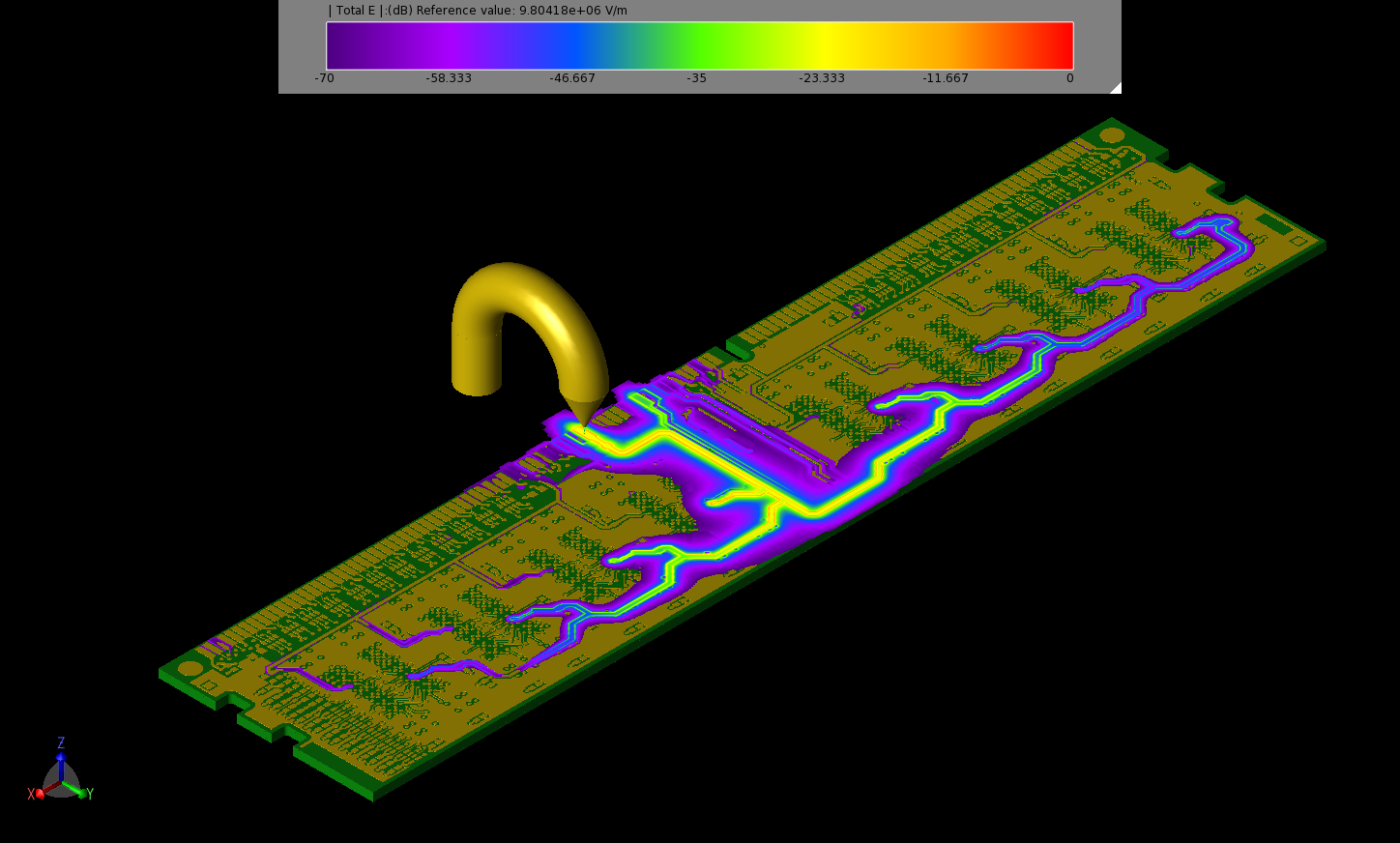

ESD 試験の手順と波形モデルは、米国規格協会(ANSI)、JEDEC、国際電気標準会議(IEC)をはじめとする数 多くの規格によって定義されています。 帯電した人間の指先から接地されたデバイスへの放電を近似する人体モデル(HBM)や、帯電したデバイスから静電ポテンシャルの低い別の導電性物体への放電を近似する帯電デバイスモデル(CDM)は、最も一般的で広く使用されている ESD モデルです。 これらのテストは一般に、ESDシミュレータ(ESDガン)を使用して、被試験デバイス(DUT)のさまざまなポイントに高速高電圧パルスを印加して実施されます。XFdtdのユーザー定義波形機能を使用すれば、さまざまな試験規格で定義されたESD波形をインポートし、それを使用してXFdtdプロジェクトでESD電流源を作成することができます。 この時点で、ESDシミュレータ/ガン・モデルを作成し、目的の位置でDUTジオメトリを励起するために使用することで、結果として生じる電磁界や電流の流れをシミュレーションおよび解析することができます。

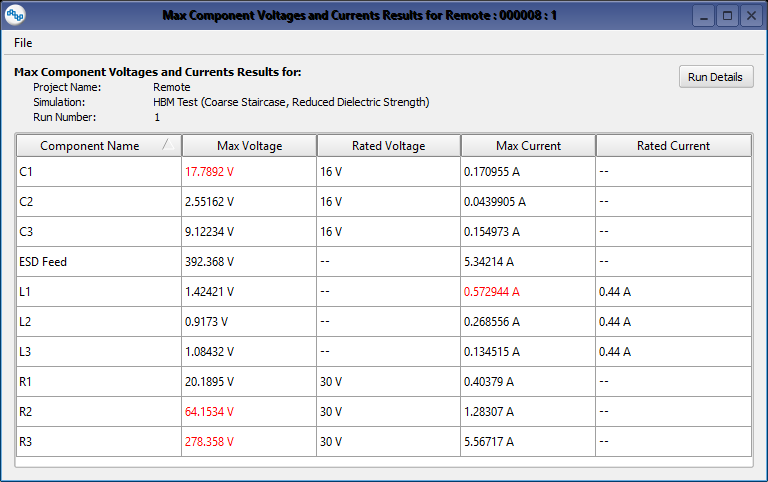

回路部品の過電圧と過電流

一般的に、回路部品の故障は、ESD試験中に誘電破壊故障よりも頻繁に発生します。 回路部品の故障を予測するには、電子部品のデータシートから入手できる定格電圧と電流の入力パラメータをXFdtdの回路部品定義に追加します。 XFdtdのシミュレーションが完了すると、定格設計パラメータを超えたコンポーネントがXFdtdの最大コンポーネント電圧および電流結果ダイアログで報告されます。

ESD緩和の最適化

シミュレーションはハードウェア・テストに完全に取って代わるものではありませんし、そうあるべきで もありませんが、ESD エンジニアに ESD 不具合の発生しやすい箇所に関する知見を提供し、ハードウェアのプロトタイ プを作成する前に ESD 緩和設計を最適化することができます。 XFdtd の機能により、ESD イベント中に誘電破壊が発生するリスクのある箇所をピンポイントで特定し、設計パラメー タを超える回路コンポーネントをレポートすることができるため、製品開発コストと市場投入までの時間が削減され、 製品の信頼性と消費者の信頼性が向上します。

追加情報

-

ウェビナー

TVSダイオードESD保護用XFdtdの過渡EM/回路コ・シミュレーション

このウェビナーでは、XFdtdの過渡電磁場/回路コ・シミュレーションが、設計プロセスの早い段階でESDの脆弱性を効果的に解消し、将来の認証の失敗を防ぐ方法をご紹介します。

探索 リソース

ウェビナー

XFdtdを用いたESD試験と損傷予測

このウェビナーでは、XFのESDシミュレーション機能を紹介し、ハードウェア・テスト前に未検出の損傷の可能性を最小限に抑える方法を実演します。

探索 リソース -

ビデオ

XFdtdの静電気放電(ESD)テスト機能のデモンストレーション

多層プリント基板を解析し、絶縁破壊の可能性がある箇所を特定するプロセスを紹介しながら、ESDテストにおけるXFの機能の使用方法を学びます。

探索 リソース -

出版物

XFdtd®の新機能

XFdtdリリース7.11.1では、シミュレーション精度の向上、解析機能の拡張、エンジニアリングワークフローの効率化を目的とした機能強化が行われています。このリリースは、アンテナ設計、PCBモデリング、フェーズドアレイシステム開発における価値の高い課題を解決するためのRemcomの継続的な取り組みを反映しています。

探索 リソース

出版物

XFdtdにおける過渡電磁界/回路コ・シミュレーション:ESD保護用TVSダイオードを詳しく見る

この論文では、3次元全波電磁界シミュレーションの強みと回路ソルバーの柔軟性を組み合わせたXFdtdの過渡電磁界/回路コ・シミュレーション機能を紹介します。

探索 リソース

出版物

静電気放電試験の時間領域シミュレーション

マイクロウェーブジャーナル誌のこの記事では、レムコムの全波電磁界シミュレーション・ソフトウェア・パッケージ、XFdtdのESDシミュレーション機能を紹介しています。ESD試験の時間領域シミュレーションについてご紹介しています。

探索 リソース