静電気放電試験の時間領域シミュレーション

静電気放電(ESD)とは、帯電した2つの物体を隔てる誘電体が破壊されることによって生じる、2つの物体間の急激な電流の流れのことである、 絶縁破壊). 電子機器の場合、結果として生じる電流の流れや火花の可能性は、機器に永久的な損傷を与える可能性があります。

静電気放電(ESD)とは、帯電した2つの物体を隔てる誘電体が破壊されることによって生じる、2つの物体間の急激な電流の流れのことである、 絶縁破壊). 電子機器の場合、結果として生じる電流の流れや火花の可能性は、機器に永久的な損傷を与える可能性があります。

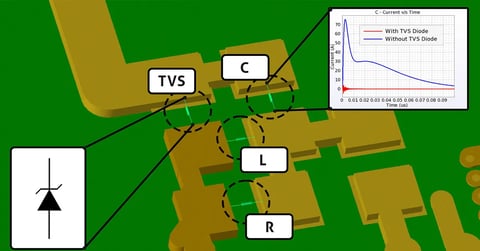

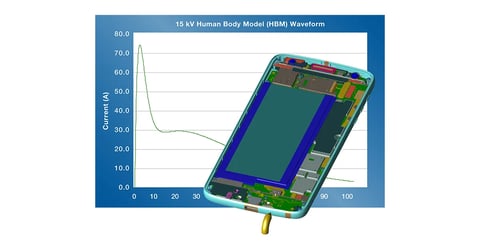

ESD は、設計・製造段階において多くのハードウェア試作品の開発・試験を必要とし、多くの保証クレーム や消費者の信頼喪失の一因となっています。 ESD によるハードウェアのテストにかかる時間と材料費の高さ、潜在故障やアプセット故障の特定 の難しさを考えると、ESD テストプロセスをシミュレートして ESD 損傷を受けやすい箇所を特定し、製品 開発のコンセプトや設計段階で ESD 緩和策を最適化する能力は非常に価値があると考えられます。

Microwave Journal誌2019年7月号の本記事では、Remcom社の全波電磁界シミュレーション・ソフトウェア・パッケージ「XFdtd EM Simulation Software」のESDシミュレーション機能を紹介する。 シミュレーションはハードウェア・テストに完全に取って代わることはできず、また取って代わるべきものでもありませんが、これらの計算機能により、ESDエンジニアはESD故障の可能性が高い箇所についてより深い知見を得ることができ、ハードウェアの試作段階に先立ってESD緩和設計を最適化することができるようになります。 レムコムは、これにより製品開発コストと市場投入までの時間を削減し、製品の信頼性と消費者の信頼を向上できると考えています。